## X-band MMIC Amplifier with Pulse-doped GaAs MESFETs

*Nobuo SHIGA, Shigeru NAKAJIMA, Kenji OTOBE, Takeshi SEKIGUCHI,

Nobuhiro KUWATA, Ken-ichiro MATSUZAKI, and Hideki HAYASHI*

Optoelectronics R&D Laboratories, Sumitomo Electric Industries, Ltd.

1, Taya-cho, Sakae-ku, Yokohama 244, JAPAN

### ABSTRACT

An X-band monolithic low noise amplifier (LNA) with  $0.5\mu\text{m}$ -gate pulse-doped GaAs MESFETs was successfully demonstrated for a direct broadcast satellite (DBS) converter. This LNA shows excellent VSWR matches of under 1.4 as well as a noise figure of 1.67dB and a gain of 24dB at 12GHz. The yield of chips within microwave specifications is 62.5%.

### INTRODUCTION

Since Japanese DBS began in 1984, households receiving DBS have been increasing, and the number has already risen above three million in Japan. R&D of consumer-adaptable MMICs such as in DBS converters is becoming vigorous today, owing to recent advances in GaAs materials and processing[1][2]. The merits of monolithic integration are miniaturization, reduction of the assembling cost and improvement of reliability. For high volume consumer application, cost is the most important problem.

The objective of this work is to develop a cost-effective and mass-produceable LNA for consumer application. GaAs MESFETs with highly doped, very narrow active regions, known as pulse-doped MESFETs, are applied for this purpose. AlGaAs/GaAs high electron mobility transistors (HEMT) are the most popular device in microwave application today, because of their excellent low noise and high gain performance. It is our view that pulse-doped MESFETs are more suitable than HEMTs from the standpoint of productivity because of their simple structure based on OMVPE-grown materials and their

easy fabrication process based on conventional photolithography techniques. Excellent low noise characteristics comparable to HEMTs with the same dimensions and high uniformity were reported, and an MMIC amplifier was also demonstrated in previous works[3][4][5].

This paper describes an LNA with improved performance and fabrication yield, which was designed with an emphasis on VSWR matches as well as a low noise figure and a high gain. To the best of our knowledge, this MMIC achieves the lowest VSWR matches with the highest yield reported so far for this kind of 12GHz monolithic LNA. Thus, troublesome cutting and pasting to tune the matching circuit can be eliminated from the assembling process of DBS converters.

### DEVICE TECHNOLOGY AND CHARACTERISTICS

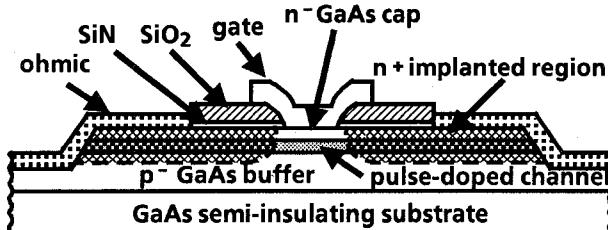

Figure 1 shows the structure of a pulse-doped GaAs MESFET. A planar structure is one of the most important factors for MMIC application to improve the uniformity and reproducibility of FET characteristics. To fabricate this structure, an undoped p-GaAs buffer layer ( $1\mu\text{m}$ ), a Si-doped GaAs active layer ( $4 \times 10^{18}/\text{cm}^3, 100\text{\AA}$ ), and an undoped n-layer ( $300\text{\AA}$ ) were successively grown by OMVPE on a semi-insulating GaAs substrate. The active areas were isolated by mesa etching. The submicron gates were defined using conventional photolithography techniques based on T-shaped dummy gate self-alignment. A T-shaped resist mask with a  $0.2\mu\text{m}$  undercut was formed by anisotropic RIE. The n+ regions were formed by the self-align implantation of Si ions. Ohmic contacts

Fig.1 : Structure of pulse-doped GaAs MESFET

were formed by evaporating Ni/AuGe and successively alloying at 450°C. Gate metals of Ti/Pt/Au were substituted for the dummy gate. The gate length was 0.5  $\mu$ m, gate metal length was 1.2  $\mu$ m and source/drain electrode spacing was 4.0  $\mu$ m.

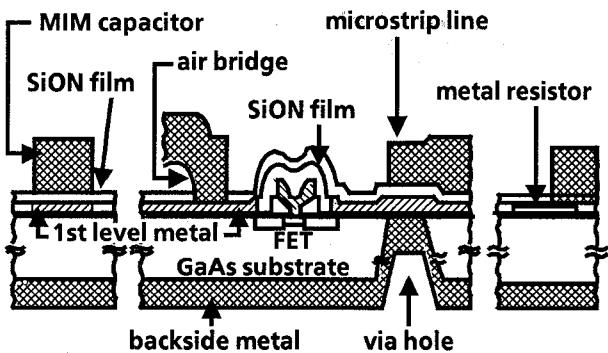

Monolithic integration was realized using via-holes for grounding, MIM capacitors employing 3000 Å thick silicon oxi-nitride, and airbridges for gate-feed circuits, etc. The substrate thickness was 100  $\mu$ m. A schematic cross-section of the MMIC structure is illustrated in Fig. 2.

Fig. 2 : Schematic cross-section of MMIC

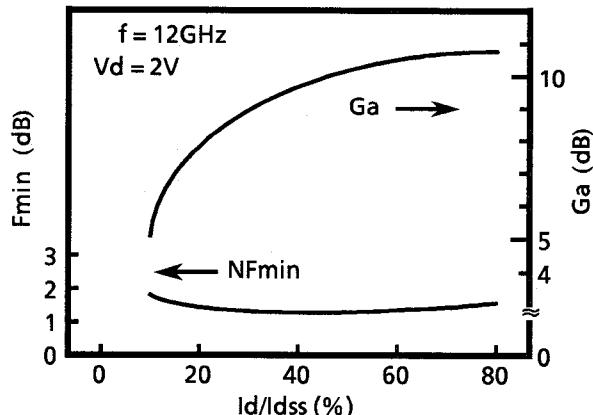

Each FET consisting of this LNA has a size of 0.5  $\mu$ m  $\times$  280  $\mu$ m. The typical DC characteristics of these devices are an  $I_{dss}$  ( $V_d=2V$ ) of 57mA with a pinch-off voltage of -1.0V and a maximum transconductance of 90mS. Figure 3 shows measured minimum noise figures ( $F_{min}$ ) and associated gains ( $G_a$ ) versus drain current ( $I_d$ ) at 12GHz. Minimum noise figures of 1.23dB with associated gains of 9.0dB were measured at 12GHz and were relatively independent of drain current. These superior features make it possible to design low noise amplifiers with a large margin for bias conditions.

Fig. 3 : Measured  $F_{min}$  and  $G_a$  versus  $I_d/I_{dss}$

## CIRCUIT DESIGN

The principal aim of the design is to attain excellent VSWR matches with high uniformity so that the LNA can be employed without any impedance tuning outside the IC. The key to the design is to optimize series feedback inductance. This is a well-known technique to achieve a simultaneous noise match and an input VSWR match, and a large margin for process fluctuations[6]. However, detailed study of the relation between FET parameters and series feedback inductance has not been extensively reported. Therefore it was examined in detail how basic parameters of a pulse-doped FET changed with the series feedback inductance using simulation and experiments[5].

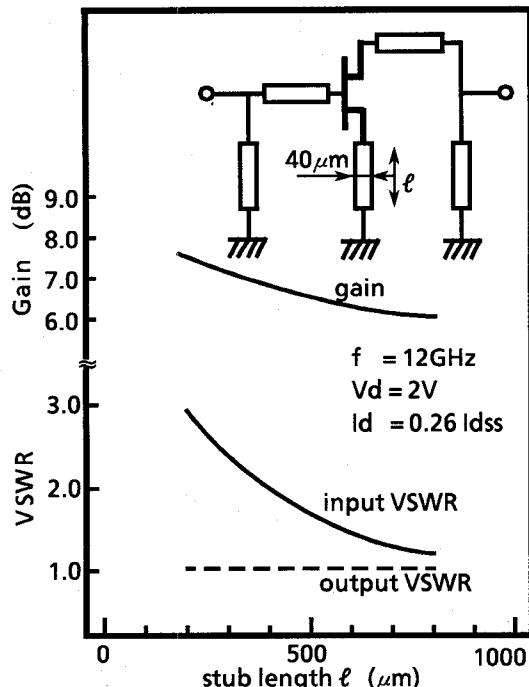

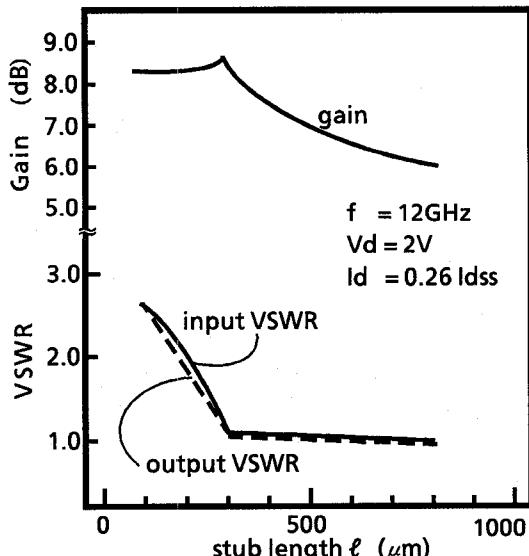

The design goal was a noise figure of less than 2.0dB, a gain of 24dB and VSWR matches of under 2.0. Based on the fundamental consideration as described above, performances of an amplifier per stage were simulated by varying stub length, because series feedback inductance was formed by a stub between the source and ground as shown in Fig. 4. Figure 4 illustrates simulation results where matching networks are synthesized so that an amplifier per stage has the minimum noise figure (called noise match below). Figure 5 shows this in the case of the maximum gain (called gain match below) as well. The first stage should be designed with noise match. The stub length needs to be more than 400  $\mu$ m to accomplish input VSWR of under 2.0 as shown in Fig. 4. 400  $\mu$ m is, however, just enough length to be

Fig. 4 : Amplifier performance for noise match

Fig. 5 : Amplifier performance for gain match

lower the input VSWR of 2.0 and there is no margin for process fluctuation. When the stub length of the first stage is set at more than 500  $\mu\text{m}$  and the following stages are designed as gain match, it is shown in Fig. 5 how many stages are needed to obtain the overall gain of the design goal. In the case of a three stage amplifier, a gain of 8.8dB per stage is needed in the following stages but figure 5 illustrates that this is impossible. Thus an amplifier which meets the design

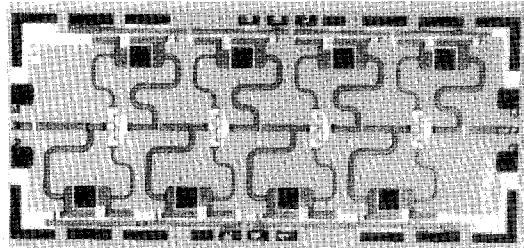

Fig. 6 : Micro-photograph of monolithic LNA

goal must have a four stage configuration. In the case of a four stage amplifier, the required gain per stage is 6dB and figures 4 and 5 show that stub lengths can be selected up to 800  $\mu\text{m}$ . From the above-mentioned study, 700  $\mu\text{m}$  was decided upon for the length of the stubs of all the stages. A micro-photograph of the LNA is shown in Fig. 6. Each stage has the same configuration because VSWRs are low enough for cascade connection.

## RESULTS

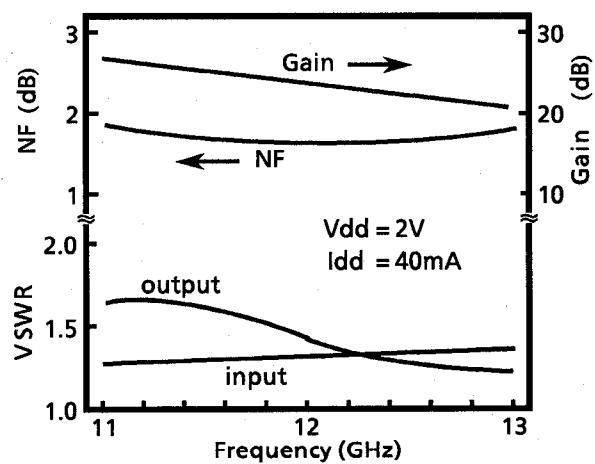

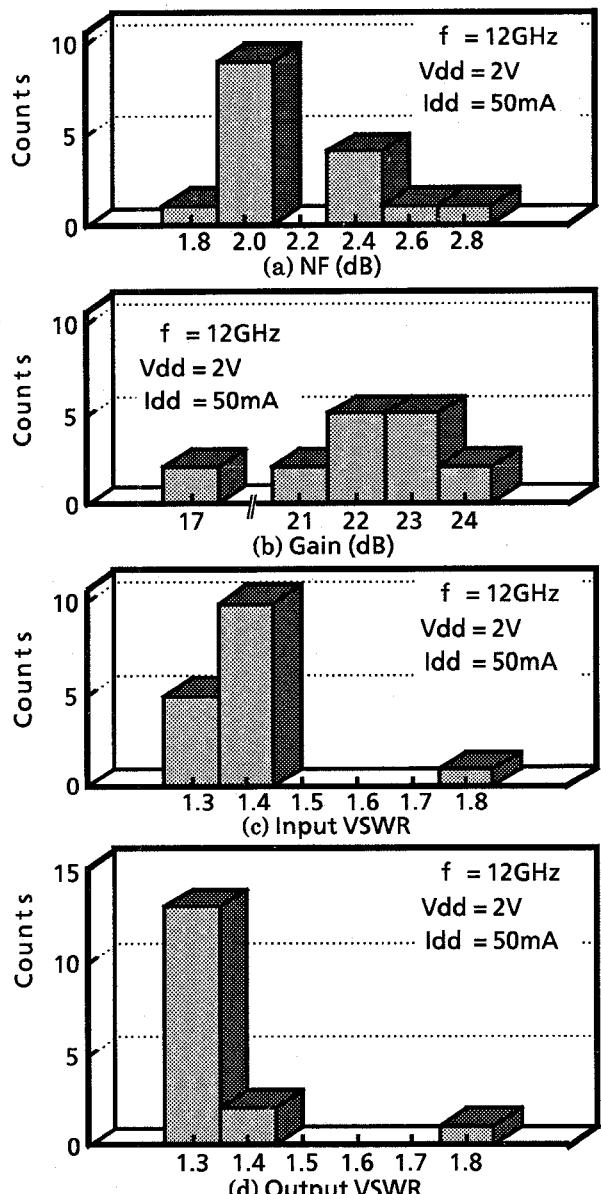

Figure 7 shows the frequency characteristics of LNA performances. It shows a very good input VSWR match of 1.3 and an output VSWR match of 1.4, as well as a noise figure of 1.67dB and a gain of 24dB at 12GHz. Figure 8 shows the distribution of the LNA performances which are from two 2-inch  $\phi$  wafers of the same lot. The noise figures of 62.5% of the chips are within 2.0dB, the gains of 75% of the chips are over

Fig. 7 : Frequency characteristics of performances

Fig. 8: Distributions of LNA performances

22dB, the input and output VSWR matches of 93.8% are under 1.4. The yield, which is defined as the percentage of chips within all the above microwave specifications, is as high as 62.5% and very high uniformity is achieved.

### CONCLUSION

An X-band MMIC Amplifier with Pulse-doped GaAs MESFETs has been successfully demonstrated. It exhibits very good VSWR matches of under 1.4 as

well as a noise figure of 1.67dB and a gain of 24dB at 12GHz with high yield of 62.5%. In the assembling process of DBS converters, the input matching network is usually tuned by cutting and pasting strip lines in order to optimize their noise figure. This LNA makes it completely unnecessary to tune anything. The results of this monolithic LNA prove that the MMIC technology based on pulse-doped MESFETs is quite promising for consumer application.

### ACKNOWLEDGEMENT

The authors would like to thank K. Nakayama, Y. Kai, K. Kawahara, K. Mukai, Y. Kawabata and S. Aoki for their technical assistance. Special thanks are due to S. Shikata, Y. Hasegawa, T. Katsuyama and M. Nishiguchi for their kind support. The authors are grateful to K. Yoshida, M. Koyama, H. Kotani, A. Ishida and K. Koe for their encouragement and support.

### REFERENCES

- [1] P. Wallace et al., "A LOW COST HIGH PERFORMANCE MMIC LOW NOISE DOWN CONVERTER FOR DIRECT BROADCAST SATELLITE RECEPTION," IEEE Microwave and Millimeter-Wave Monolithic Circuits Symposium Digest, pp.7-10, 1990.

- [2] N. Ayaki et al., "A 12GHz-Band Super Low-Noise Amplifier Using A Self-Aligned Gate MESFET," IEEE Microwave and Millimeter-Wave Monolithic Circuits Symposium Digest, pp.7-10, 1989.

- [3] S. Nakajima et al., "OMVPE grown GaAs MESFETs with step-doped channel for MMICs," GaAs IC Symposium Digest, pp.297-300, 1988.

- [4] S. Nakajima et al., "Pulse-doped GaAs MESFETs with planar self-aligned gate for MMIC," IEEE Int. Microwave Symposium Digest, pp.1081-1084, 1990.

- [5] N. Shiga et al., "X-Band Monolithic Four-stage LNA with Pulse-doped GaAs MESFETs," GaAs IC Symposium Digest, pp.237-240, 1990.

- [6] R. Lehmann et al., "X-Band Monolithic Series Feedback LNA," IEEE Trans. on Microwave Theory and Tech., Vol. MTT-33, pp.1560-1566, Dec., 1985.